|

Tutorial 1 (T1):

Title: OTFS: A New Modulation Scheme for 5G and BeyondDownload

Speaker: Prof. A. Chockalingam, Department of ECE, IISc, Bangalore

Schedule: 02:00 PM-05:00 PM, Feb. 21, 2020

Abstract:

Next generation wireless systems are envisioned to support high-speed communications with high reliability and energy efficiency in various wireless environments. 5G wireless communication technology is expected to provide seamless and consistent high-mobility user experience in a variety of scenarios that include high-speed/bullet trains (200-500 km/h speed in sub-6 GHz bands) and aircrafts. Also, 5G technology is expected to operate in extremely heterogeneous environments and offer enhanced mobility support compared to 4G technology. Enabling high-speed and reliable communication in high-mobility scenarios requires techniques which are specially suited for the dynamic nature of the underlying channel. The wireless channels in such scenarios are rapidly time-varying and hence doubly-dispersive in nature, with the multipath effects causing time dispersion and Doppler shifts causing frequency dispersion. Conventional multicarrier modulation techniques are primarily designed to combat the multipath effects that cause inter-symbol interference (ISI). However, communication in high-mobility scenarios and communication using mmWave frequencies (e.g., 28 GHz) in low-to-medium mobility scenarios encounter high Doppler shifts and the consequent degrading effects of inter-carrier interference (ICI) in conventional multicarrier modulation schemes (such as OFDM).

Orthogonal time frequency space (OTFS) modulation is a recently introduced new modulation scheme suited for doubly-dispersive wireless channels. It is a 2-dimensional (2D) modulation scheme designed in the delay-Doppler domain, unlike traditional modulation schemes which are designed in the time-frequency domain. It multiplexes the information symbols in the delay-Doppler (DD) domain. This is in contrast to conventional multicarrier modulation schemes which multiplex symbols in the time-frequency (TF) domain. Also, the channel response is viewed in the DD domain as opposed to viewing it in the TF domain. An advantage of the DD representation of wireless channels is that the rapid fluctuations in time-varying channels exhibit slow variations when viewed in the DD domain. This, along with the fact that the channel in the DD domain has a sparse nature, simplifies channel estimation in rapidly time-varying channels. The slow variability of the DD channels reduces the overhead of frequent channel estimation in channels with small coherence times. Another attractive feature of OTFS is that it could be architected with pre- and post processing operations over any existing multicarrier system. It has been shown that OTFS offers significant performance advantages compared to OFDM in point-to-point and multiuser environments.

This tutorial will introduce OTFS modulation and highlight the various signal processing functions in the delay-Doppler domain and transforms needed for OTFS modulation implementation. OTFS signal detection methods and channel estimation techniques (using pilot symbols embedded in the delay-Doppler domain) will be presented. Performance comparison between OTFS and OFDM in SISO and MIMO settings will be highlighted. The talk will also highlight the peak-to-average power ratio (PAPR) characteristics of OTFS in comparison with that of OFDM. Multiuser communication using OTFS, where resource blocks in the delay-Doppler grid, called delay-Doppler resource blocks (DDRBs), are allocated to different users will be discussed. Performance advantage of OTFS multiple access (OTFS-MA) compared to OFDMA and SC-FDMA will be highlighted. Potential topics of OTFS research will be highlighted.

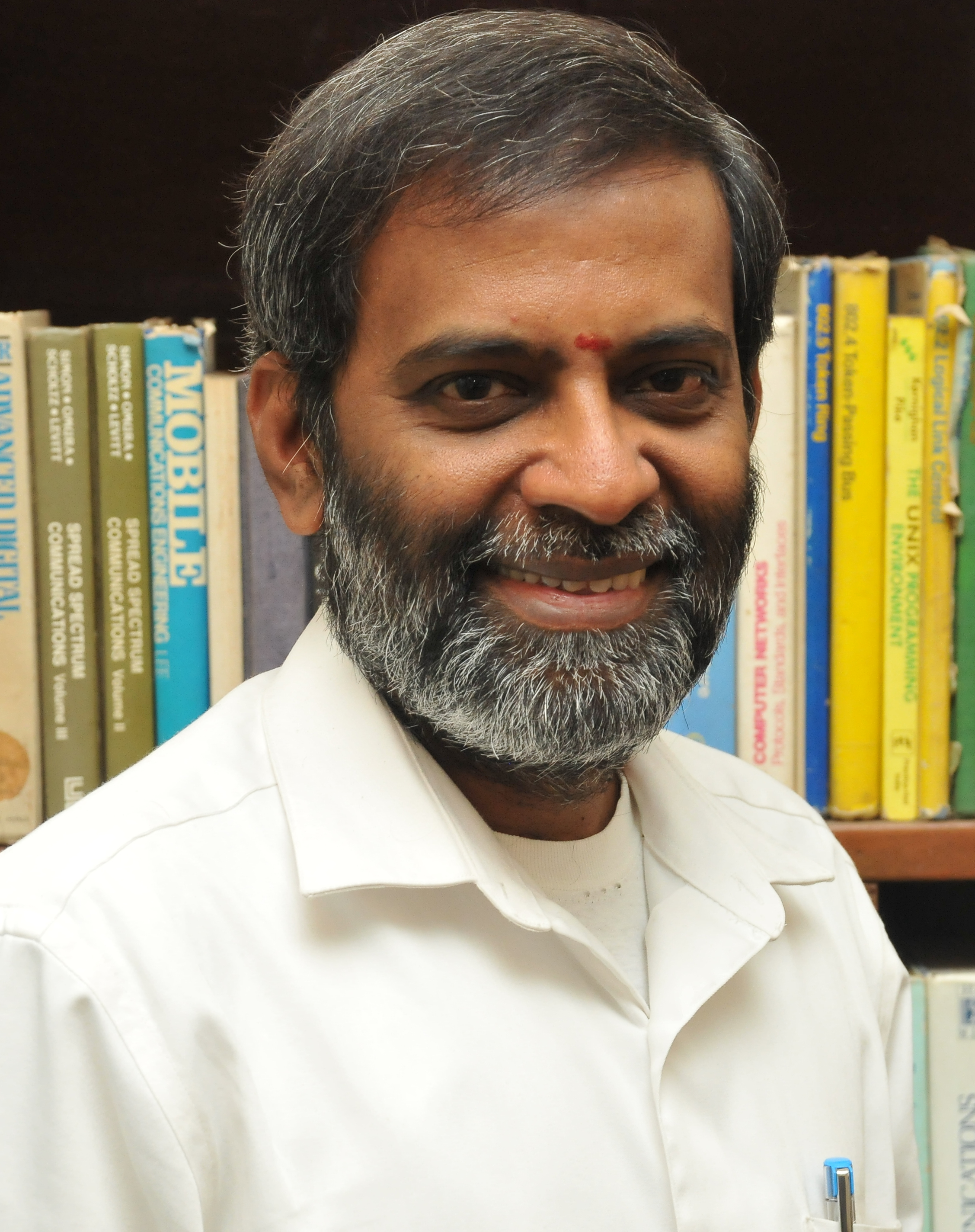

Speakers Biography:

A. Chockalingam received the B.E. (Honors) degree in ECE from P.S.G. College of Technology, Coimbatore in 1984 and the M.Tech degree in E & ECE from IIT, Kharagpur in 1985. In 1993, he obtained the Ph.D. degree in ECE from IISc, Bangalore. From Dec.1993 to May 1996, he was a Postdoctoral Fellow and an Assistant Project Scientist with the Department of ECE, University of California San Diego. From May 1996 to Dec. 1998, he was with Qualcomm, San Diego, as a Staff Engineer/Manager. Currently, he is a Professor in the Department of ECE, IISc, Bangalore.

|

|

Tutorial 2 (T2):

Title: Signal Processing and Deep Learning on Graphs

Speaker: Dr. Sundeep Prabhakar Chepuri , Department of ECE, IISc, Bangalore

Schedule: 02:00 PM-05:00 PM, Feb. 21, 2020

Abstract:

Graphs are mathematical objects that may be used for explaining relationships in many complex datasets, which are frequently encountered in many scientific disciplines. Unlike regular domains (e.g., time series or images, where the data is indexed by time ticks or pixels), data collected on networks or manifolds are indexed by an arbitrary enumeration and the underlying irregular domain structure can be described using graphs. Such graph- structured data are generated from platforms like environmental sensing, medical and brain imaging systems, social networking and e-commerce sites, to list a few. To extract meaningful information from graph-structured data, several concepts and tools are being developed in the emerging research fields of graph signal processing and geometric deep learning.

Graph signal processing research extends traditional signal processing concepts developed to represent, interpret, and analyze data collected on regular domains to signals defined on graphs and irregular (or, geometric non-Euclidean) domains. Deep learning methods, mainly deep convolutional neural networks (CNN) and recurrent neural networks (RNN), are very popular machine learning techniques that have recently proven to be very successful for solving complicated inference problems especially when large amounts of data are available. Using advances in graph signal processing, specifically, using the definition of convolutions and filters on graphs, deep learning algorithms have been generalized as geometric deep learning, formalized as graph convolutional neural networks (GCNN), to apply learning on graph-structured data.

In this tutorial, the main focus will be on graph signal processing and graph neural networks. We will discuss concepts such graph filters, graph sampling and recovery, and graph topology inference. Then, we will discuss convolutional neural networks and recurrent neural networks for graphs-structured data.

Speakers Biography:

Sundeep Prabhakar Chepuri received his M.Sc. degree (cum laude) in electrical engineering and Ph.D. degree (cum laude) from the Delft University of Technology, The Netherlands, in July 2011 and January 2016, respectively. He was a Postdoctoral researcher at the Delft University of Technology, The Netherlands, a visiting researcher at University of Minnesota, USA, and a visiting lecturer at Aalto University, Finland. He has held positions at Robert Bosch, India, during 2007- 2009, and Holst Centre/imec-nl, The Netherlands, during 2010-2011. Currently, he is an Assistant Professor at the Department of ECE at the Indian Institute of Science (IISc) in Bengaluru, India.

Dr. Chepuri was a recipient of the Best Student Paper Award at the IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP) in 2015, Best Student Paper Award (as co-author) at ASILOMAR 2019, and the Pratiksha Trust Young Investigator award. He is currently an Associate Editor of the EURASIP Journal on Advances in Signal Processing, and an elected member of the EURASIP Technical Area Committee (TAC) on Signal Processing for Multisensor Systems.

|

|

Tutorial 3 (T3):

Title: Energy Harvesting and RF Energy Transfer aided Sustainable IoT Networks

Download Part1 Download Part2

Speaker: Prof. Swades De, Department of EE, IIT Delhi

Schedule: 09:00 AM-12:00 PM, Feb. 21, 2020

Abstract:

The interests in wireless connectivity is ever-increasing and the needs for automated remote access, monitoring, and control are well-appreciated. However, widespread adoption of networked wireless devices or Internet of Things (IoT) nodes is largely constrained by their affordable deployment and maintenance costs and convenience of their long-term usage. In particular, in IoT communication networks, one of the main constraints is energy sustainability, as the wireless end nodes are characterized by limited energy resources.

In this discourse, considering a few typical application contexts, we will first discuss the contemporary approaches and optimization techniques for energy-efficient IoT communication with energy-constrained wireless devices. The contexts with ambient energy harvesting sources and energy-harvesting aware architectures as well as node-level and network protocol solutions will also be discussed. Subsequently, we will present the communication and networking propositions with dedicated on-demand wireless energy supply. We will specifically consider the cases of energy replenishment with radio frequency energy transfer (RFET). We will discuss two-dimensional (terrestrial mobile energy agent aided) as well as three-dimensional (unmanned aerial vehicle aided) RFET and joint RFET and information exchange approaches towards sustainable IoT networks. Throughout the discourse, from our research experience we will take a few example cases of state-of-the-art research solutions on energy-efficient and energy-harvesting network systems.

Speakers Biography:

Dr. Swades De is a Professor in the Department of Electrical Engineering at Indian Institute of Technology Delhi. Dr. De's research interests are broadly in communication networks, with emphasis on performance modeling and analysis. Current directions include energy harvesting communication networks, broadband wireless access and routing, cognitive/white-space access networks, smart grid networks, and IoT communications.

Dr. De is currently an Area Editor for the IEEE COMMUNICATIONS LETTERS and an Associate Editor respectively for the IEEE TRANSACTIONS ON VEHICULAR TECHNOLOGY, IEEE WIRELESS COMMUNICATIONS LETTERS, IEEE NETWORKING LETTERS, and the IETE Technical Review Journal. Dr. De is a fellow of INAE (Indian National Academy of Engineering), and NASI (The National Academy of Sciences, India), respectively, and a senior member of the IEEE, and IEEE Communications and Computer Societies.

|

|

Tutorial 4 (T4):

Title: SGD and Friends Download

Speaker: Prof. Ketan Rajawat, Department of EE, IIT Kanpur

Schedule: 09:00 AM-12:00 PM, Feb. 21, 2020

Abstract:

This tutorial delves into the world of Stochastic Gradient Descent (SGD) algorithm and its many variants that have been widely utilized in large-scale signal processing, machine learning, and communications. Early appearances of SGD include the Stochastic Approximation framework by Robbins-Monro in 1951, LMS algorithm for adaptive filtering by Widrow-Hoff in 1960, Perceptron classifier by Rosenblatt in 1957, and SVM classifier by Cortes-Vapnik in 1995. In the last decade, SGD has been widely used for training large-scale supervised learning models, even in settings where the training problem is non-convex and non-differentiable, such as in neural networks. Recent years have seen several attempts at explaining and specializing SGD to a variety of settings.

In the modern context, iteration complexity analysis is the de facto standard for studying and comparing the plethora of SGD variants. Such analysis allows us to obtain bounds on the total number of stochastic gradients required to reach a certain pre-specified accuracy and is useful for identifying the correct regime under which a particular variant works. This tutorial will provide a principled introduction to SGD iteration complexity analysis for the signal processing, machine learning, and communications audience. The tools covered here should enable the audience to modify the existing proofs for their applications of interest.

Additionally, the tutorial seeks to update the audience with all the state-of-the-art SGD variants. Beyond the classical SGD, we will analyze variance-reduced, compressed, distributed, asynchronous, and momentum-based versions, most of which have appeared only in the last two years. Different from the proofs presented in the corresponding seminal papers that tend to follow disparate styles, we will attempt to provide a few common analysis techniques that will serve to unify these approaches. The tutorial will conclude with a list of “low-hanging fruits” in the broad area of SGD and online learning.

Speakers Biography:

Ketan Rajawat (S’06–M’12) received his B.Tech and M.Tech degrees in Electrical Engineering from the Indian Institute of Technology (IIT) Kanpur, India, in 2007, and his Ph.D. degree in Electrical and Computer Engineering from the University of Minnesota, Minneapolis, MN, USA, in 2012. He is currently an Assistant Professor in the Department of Electrical Engineering, IIT Kanpur. His research interests are in the broad areas of signal processing, robotics, and communications networks, with particular emphasis on distributed optimization and online learning. His current research focuses on the development and analysis of distributed and asynchronous optimization algorithms, online convex optimization algorithms, stochastic optimization algorithms, and the application of these algorithms to problems in machine learning, communications, and smart grid systems. He is currently serving as an Associate Editor with the IEEE Communications Letters. He is also the recipient of the 2018 INSA Medal for Young Scientists and the 2019 INAE Young Engineer Award.

|

|

|

Tutorial 5 (T5):

Title: Integrated Transceiver Architectures for 5G Cellular Base Stations Download

Speaker: Dr. Jaiganesh Balakrishnan, Mr. Sriram Murali, Texas Instruments, Bangalore

Schedule: 09:00 AM-12:00 PM, Feb. 21, 2020

Abstract:

5G cellular network technologies offer increased channel capacity and data rates by employing massive MIMO, higher bandwidth, as well as new frequency bands. High-performance system-on-chip transceiver products, which integrate the RF/analog/digital signal processing front-ends and support multiple transmit, receive and feedback channels in a single device, with low power consumption, are key enablers in the deployment of 5G cellular base stations.

Products incorporating recent advances in high-performance integrated transceivers, which employ different signal chain architectures to cater to massive MIMO and mm-wave 5G technologies, have been key enablers to the commercial deployment of 5G cellular base stations. A zero-IF architecture is best suited for single band massive MIMO systems, requiring signal bandwidth support of a few 100s of MHz. An RF-sampling architecture, incorporating multi-GSPS high-performance data converters that directly sample the RF signal, is highly flexible, as it enables support for very wide signal bandwidths, in the order of GHz, as well as simultaneous multi-band transmission and reception.

This industry tutorial will introduce technology trends and practical constraints driving the architecture choices for integrated transceivers in 5G cellular base stations. We present an overview of the IF-sampling architecture used in legacy 3G/4G base stations, introduce advances related to zero-IF and RF-sampling architectures, and present system level trade-offs associated with each of these architectures that influences their suitability for different classes of 4G/5G base stations. We discuss the impact of RF/analog impairments, arising from practical IC designs, on critical system parameters of interest for wireless base stations. We also discuss practical challenges in the design of high-performance, low-power integrated transceiver SoC products employing these architectures and present various signal processing algorithms and digital design techniques to address these challenges. Specifically, we address aspects related to I/Q imbalance, ADC interleaving mismatch, transmit carrier leakage, automatic gain control and other system calibrations.

Speakers Biography:

Dr. Jaiganesh Balakrishnan is a Principal Architect and Fellow with the Analog Signal Chain department at Texas Instruments, Bangalore. He received his B.Tech in Electrical Engineering from IIT, Madras, in 1997, and Ph. D in Electrical and Computer Engineering from Cornell University, USA, in 2002. At TI, his research has been in the field of Signal Chain Architectures, Signal Processing Algorithms and Communication Systems on technologies spanning 4G/5G base stations, GPS/WLAN/FM transceivers, DVB-H and UWB. Jaiganesh has developed architectures/algorithms for various highly integrated high performance and low power consumption system-on-chip solutions, for mobile handsets and wireless base stations. He holds

70+ patents and is the recipient of the 2010 TR35 Young Innovator award by MIT’s Technology Review Magazine.

Sriram Murali is a Principal Engineer and Senior Member of Technical Staff with the Wireless Infrastructure Business Unit at Texas Instruments, Bangalore. He received a B.Tech. in Electrical Engineering from IIT Madras in 2001, and an MS in Electrical Engineering from California Institute of Technology, USA, in 2002. His research interests are in architectures and algorithms for signal processing and communication systems. He has worked on highly integrated high

performance and low power SoC products including 4G/5G transceivers, Automotive Radar, Low-power WLAN, Vehicular/Pedestrian Navigation, and FM transceivers. He has over 15 patents granted by the US Patent Office.

|

|

Tutorial 6 (T6):

Title: Hands-On Tutorial: Design and prototype SDR systems with MATLAB and Simulink

Speaker: Mr. Tabrez Khan, Ms. Hitu Sharma, MathWorks India

Schedule: 02:00 PM-05:00 PM, Feb. 21, 2020

Abstract:

The latest innovation in wireless communications brought the complexity of highly integrated digital, RF and antenna technologies. Many engineering teams designing such wireless complex applications recognize that they need a single integrated development environment to prevent isolated component designs, minimize error-prone implementation, and avoid expensive hardware verification.

Using MATLAB® and Simulink®, users can model and simulate end to end wireless communication system, integrate Analog Devices AD9361 RF Agile Transceiver™ as RF Front end and prototype on Xilinx® Zynq®-7000 All Programmable SoC.

Outcome:

In this 3-hour hands-on tutorial, you will learn how to:

- Model and simulate radio designs.

- Verify algorithms in simulation with streaming RF data

- Deploy radio designs on Zynq-based hardware with HDL and C-code generation.

- Participants will be provided trial licenses for MATLAB and relevant products prior to the event.

Speakers Biography:

Tabrez Khan is a senior application engineer with MathWorks India specializing in the domain of signal processing and wireless communications. He has over 16 years of industry experience and has worked with various customers in Aerospace & Defense, Communications, Electronics, Semiconductor and Education industry to help them adopt MATLAB and Simulink based products in their signal processing and wireless communication applications. He holds Master’s degree in Digital Electronics & Communication from NMAMIT, Nitte & Bachelor’s degree in Electronics & Communication from BIET, Kuvempu University, Karnataka.

Hitu Sharma is a part of Application Engineering Group at MathWorks focusing on Signal processing and FPGA Prototyping. She has been supporting number of government and commercial establishments pan India for projects based on Signal Processing and Communication. She has been involved with educational establishments for Faculty development programs and project-based learning on low cost hardware. She has 11+ years of experience in FPGA based prototyping, product development and embedded design development (Linux/Windows) with AeroDef Industry.

Prior to joining MathWorks Hitu Sharma has worked as design engineer with HCL, TATA Advanced Systems and as a Senior R & D engineer for two startups. She has prototyped a serial cryptographic unit and a technical key generation unit. She as designed IP cores for cryptographic algorithms and Digital receiver chain for the ground surveillance RADAR systems. She has represented her work on many platforms, including Defense EXPO. Her areas of interest include FPGA design, Signal processing, and Digital Communication. She holds a bachelor’s degree in Electronics and Communication Engineering.

|